信号と電力の完全性:時間と周波数領域

2.13帯域幅とクロック周波数

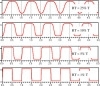

これまで見てきたように、帯域幅は信号の立ち上がり時間に関連しています。 クロック周波数はまったく同じですが、立ち上がり時間と帯域幅が異なり、2つの異なる波形を持つことができます。 クロック周波数を知っているだけでは、帯域幅が何であるかを知ることはできません。 図2-14は、4つの異なる波形を示しており、それぞれが1GHzのクロック周波数とまったく同じです。 ただし、立ち上がり時間が異なり、したがって帯域幅が異なります。

図2-14 4つの異なる波形、それぞれがまったく同じ1GHzのクロック周波数。 それらの各々は、周期の割合として異なる立ち上がり時間を有し、したがって異なる帯域幅を有する。

信号の立ち上がり時間が必ずしもわからないことがありますが、とにかく帯域幅のアイデアが必要です。 単純化した仮定を使用して、クロック周波数だけからクロック波の帯域幅を推定することができます。 それでも、帯域幅を決定するのはクロック周波数ではなく、立ち上がり時間であることに注意することが重要です。 波形について知っているのがクロック周波数だけであれば、帯域幅を確実に知ることはできません。

信号の帯域幅をそのクロック周波数だけから評価するには、非常に重要な仮定をする必要があります。 クロック波の典型的な立上り時間を推定する必要があります。

実際のクロック波形では、立ち上がり時間はクロック周期とどのように関係していますか? 原則として、唯一の関係は、立ち上がり時間が期間の50%未満でなければならないということです。 これ以外にも、制限はなく、立ち上がり時間は、周期の任意の端数とすることができる。 これは、クロック周波数がデバイス技術の限界を押し進めている場合のように、1GHzのクロックのように、期間の25%になる可能性があります。 これは、多くのマイクロプロセッサベースの製品に典型的な期間の10%である可能性があります。 これは、外部の低クロック周波数メモリバスを駆動するハイエンドFpgaに見られる期間の5%である可能性があります。 ボードレベルのバスが従来のシステムであれば、1%になる可能性もあります。

立ち上がり時間がどの期間の割合であるかわからない場合、合理的な一般化は、立ち上がり時間がクロック期間の7%であるということです。

立ち上がり時間がどの期間の割合であるかがわからない場合、合理的な一般化は これは、多くの一般的なマイクロプロセッサベースのボードとボードレベルのバスを駆動するAsicに近似します。 このことから、クロック波形の帯域幅を推定することができます。

この上昇時間が期間の7%であるという仮定は少し積極的であることに留意すべきである。 ほとんどのシステムはおそらく10%に近いため、通常よりもわずかに短い立上り時間を想定しています。 同様に、立ち上がり時間を過小評価している場合は、帯域幅を過大評価することになりますが、これは過小評価するよりも安全です。

立ち上がり時間が期間の7%の場合、期間は1/0.07または立ち上がり時間の15倍になります。

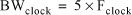

立ち上がり時間が期間の7%の場合、期間は1/0.07ま 帯域幅については、0.35/立ち上がり時間として近似しています。 クロック周波数はクロック周期の逆数であるため、クロック周波数をクロック周期に関連付けることができます。 クロック周波数のクロック周期を置き換えると、最終的な関係になります。

式2-5

ここで、

- BWclock=クロックのおおよその帯域幅(GHz)

- Fclock=クロック繰り返し周波数(GHz)

例えば、クロック周波数が100mhzの場合、信号の帯域幅は約500MHzです。 クロック周波数が1GHzの場合、信号の帯域幅は約5GHzです。

これは、立ち上がり時間がクロック周期の7%であるという仮定に基づいた一般化と近似です。 この仮定を考えると、これは非常に強力な経験則であり、非常に少ない労力で帯域幅の推定値を与えることができます。 これは、クロック波の中で最も高い正弦波周波数成分は、典型的には第五高調波であると言います!

明らかですが、繰り返しますが、帯域幅を評価するために常に立ち上がり時間を使用したいと考えています。 残念ながら、波形の立ち上がり時間を知ることは必ずしも贅沢ではありません。 そして、まだ、我々は今答えが必要です!